Study Power Point प्राविधिक शिक्षा परिषद् उ॰ प्र॰ द्वारा

स्वीकृत नवीनतम् पाठ्यक्रमानुसार

# डोजटल इलेक्ट्रानिक्स

(DIGITAL ELECTRONICS)

R. M. Upadhyay

WHOLESALE - RETAILERS OF COMPETITION BOOKS

यन्द्रभाता पुरतक भण्डार

भगत सिंह मार्ग, सहारनपुर (M) 9897783803, 9045400004

प्राविधिक शिक्षा परिषद् उत्तर प्रदेश द्वारा स्वीकृत नवीनतम पाठ्यक्रमानुसार

# डिजिटल इलैक्ट्रॉनिक्स

प्रयोगात्मक कार्य सहित

# [DIGITAL ELECTRONICS]

**With Practicals**

[द्वितीय वर्ष (तृतीय सेमेस्टर) इलैक्ट्रिकल इंजीनियरिंग एवं इलैक्ट्रॉनिक्स इंजीनियरिंग के विद्यार्थियों के लिए]

राहुल मणि उपाध्याय

(M. Tech.)

प्रवक्ता इलैक्ट्रॉनिक्स बुद्धा इन्सट्रीटयूट ऑफ टेक्नोलॉजी गोरखपुर

# जय प्रकाश नाथ पिटलकेशन्स

गाँधी आश्रम चौराहा नौचन्दी रोड, मेरठ - 250 002 (यू० पी०)

जय प्रकाश नाथ पब्लिशन्स

गाँधी आश्रम चौराहा, नौचन्दी रोड, मेरठ (उ० प्र०) 250 002

फोन: (0121) 2762403, 4056123

टेली फैक्स : 0121-2600606

email: jpnpmrt@hotmail.com

: info@jpnpbooks.com Web : www.jpnpbooks.com

डिजिटल इलैक्ट्रॉनिक्स का कोई भी अंश लेखक एवं प्रकाशक की पूर्व लिखित अनुमित के बिना किसी भी रूप में उद्घृत या प्रकाशित नहीं किया जा सकता।

• लेखकगण

0

प्रथम संस्करण : 2019-20

Abhishek Kumar

• मूल्य : 175.00

लेजर टाइपसैटर्स :

श्री राम कम्प्यूटर्स मेरठ।

मुद्रक :सनी ऑफसैटमेरठ।

#### प्रस्तावना

प्राविधिक शिक्षा परिषद् लखनऊ द्वारा संशोधित नवीनतम् पाठ्यक्रम पर आधारित डिप्लोमा इंजीनियरिंग के पाठ्यक्रम के लिए यह पुस्तक ''**डिजिटल इलेक्ट्रॉनिक्स**'' आपके सम्मुख है।

छात्र एवं छात्राओं की परेशानियों को ध्यान में रखते हुए पुस्तक को इस प्रकार से लिखा गया है कि अंग्रेजी माध्यम के छात्र एवं छात्रायें भी इसे आसानी से समझ सकें। इसके साथ-साथ हिन्दी माध्यम के छात्र-छात्रायें भी तकनीकी ज्ञान को अंग्रेजी में खोये बिना, हिन्दी में समझ सकते हैं, जिससे आने वाली समस्या का सामना आसानी से कर सकते हैं क्योंकि पुस्तक में प्रयुक्त भाषा भी इस प्रकार रखी गई है कि हिन्दी भाषी छात्रों को तकनीकी विषय समझने में असुविधा न हो। अंग्रेजी में बोले जाने वाले शब्दों को अंग्रेजी में ही लिखा गया है।

इस पुस्तक को तैयार करते समय विभिन्न विद्वान मित्रों एवं शिक्षकों के मार्गदर्शन एवं बहुमूल्य सुझाव प्राप्त हुए हैं। हम उनका हृदय से आभार व्यक्त करते हैं।

इस पुस्तक के लेखन में जिन महानुभावों का प्रत्यक्ष अथवा अप्रत्यक्ष रूप से योगदान रहा है उनमें श्री आर० ए॰ अग्रवाल (चेयरमैन BIT, Gorakhpur), श्री रजत अग्रवाल (सेकरेट्री BIT, Gorakhpur), श्री सुधीर अग्रवाल (BIT, Gorakhpur) पाटेश्वरी सिंह (प्रधानाचार्य M.P. Polytechnic), निशांत त्रिपाठी (Deputy Director NIELIT, Gorakhpur), श्री डी॰ पाल (प्रवक्ता गणित), श्री रूदल सिंह (प्रवक्ता मैकेनिकल इंजी॰), प्रेरणा गर्ग (एम॰ पी॰ पॉलीटेक्निक, स्व॰ वि॰ पो॰), अर्पित सिंह (एम॰ पी॰ पा॰, स्व॰ वि॰ पो॰), श्री बी॰ एन॰ चौधरी (राजकीय पा॰, गोरखपुर), श्री अखिलेश चतुर्वेदी (जी॰ पी॰ बस्ती), श्री पीयूष शाक्य (जी॰ पी॰ कानपुर), श्री एन॰ पी॰ सिंह (जी॰ पी॰ मिर्जापुर), श्री बी॰ के॰ सिंह (प्रधानाचार्य जी॰ पी॰ गाजीपुर), श्री सुधीर कन्नौजिया (डी॰ आई॰ टी॰ एम॰ महाराज्यांज), श्री लवकुश सिंह (राजकीय पा॰ बाँदा), श्री अजय सिंह (प्रसाद पा॰ जौनपुर), श्री अंकुर श्रीवास्तव (लि॰ फ॰ पा॰ गोरखपुर), विवेकराव (महामानव पॉलीटेक्नीक, गोरखपुर) श्री अंकुर मिश्रा (एम॰ पी॰ पा॰, स्व॰ वि॰ पो॰), श्री पवन तिवारी, चन्द्रेश कुमार, प्रीति श्रीवास्तव, प्रियदर्शिनी, राहुल सिंह, शिवाकान्त दूबे, सत्यम कुमार मल्ल, प्रियंका, श्री अनिमेष कुमार, निशा श्रीवास्तव, श्रिखा श्रीवास्तव, प्रिया गरिमा पाण्डेय, कृष्णा पाण्डेय, श्री नीरज पाण्डेय, स्व॰ राजीव कुमार श्रीवास्तव एवं श्री विनोद कुमार श्रीवास्तव के नाम उल्लेखनीय हैं।

जीवन में माता-पिता तथा गुरुजनों का कोई विकल्प नहीं है। आपका हृदय से धन्यवाद।

हम विशेष रूप से अपने माता-पिता ''श्रीमती पुष्पलता उपाध्याय एवं श्री मानस मणि उपाध्याय'' के आभारी हैं जो कि इस पुस्तक के लिए हमारे प्रेरणास्रोत रहे हैं।

इसके साथ-साथ हम पुस्तक के प्रकाशक, श्री वी० एन० गुप्ता, श्री आर० एन० गुप्ता ''जय प्रकाश नाथ पब्लिकेशन्स'', मेरठ एवं उनके परिवार के हृदय से आभारी हैं। आपके सहयोग के बिना यह संस्करण संभव नहीं था।

-लेखक

Email Id : rahulmaniupadhyay@gmail.com Mob. No. 9451885710

पूज्ता्य म्रात्राज्रा प्रित्राज्रा स्रादर स्याप्त

# Study Power Point SYLLABUS

#### Rationale

Digital electronics has made extremely rapid advances in the last five decades. It has Digital electronics has made extremely applications in communication entertainment, instrumentation, control important applications in communication end to its usefulness. In fact, the light important applications in communication and to its usefulness. In fact, the light and the automation etc. Thus it appears that there is no end to its usefulness. In fact, the light and the automation etc. Thus it appears that there to give the knowledge of digital electronics to the new world belong to it. So it is necessary to give the knowledge of digital electronics to the new world belong to it. So it is necessary to get exciting technological advancement electrical students. Microprocessor is one of the most exciting technological advancement electrical students. Microprocessor is one statement and students among the semiconductor devices in recent times. It has a tremendous impact on the Industrial among the semiconductor devices in recent times. among the semiconductor devices in recent that and control capacity both at the design and the processes due to its high reliability, flexibility and control capacity both at the design and the processes due to its high renability, head with increasing facilities act as catalysis; widening their scope of applications.

> LTP 5 - 4

1. Number Systems

(10 Periods)

- 1.1 Decimal, binary, octal and hexa-decimal number system and their inter-conversion

- 1.2 Binary and Hexadecimal addition, subtraction and multiplication.

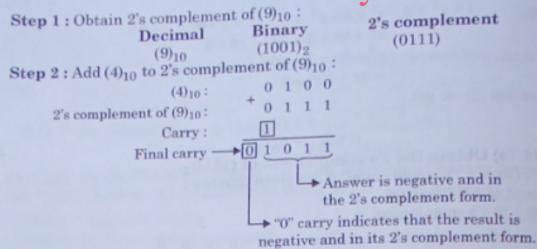

- 1.3 1's and 2's complement methods of addition/subtraction.

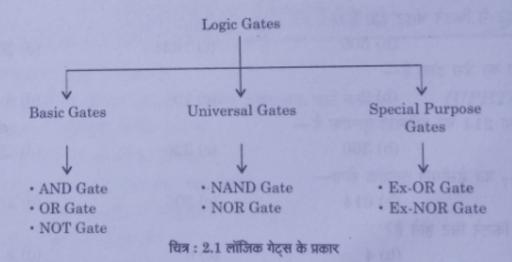

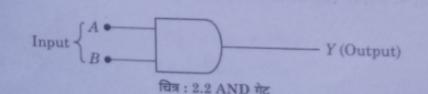

2. Gates

(08 Periods)

Definition, symbol and truth tables for inverter, OR, AND, NAND, NOR and X-08 exclusive-AND gates

3. Boolean Algebra

(12 Periods

- 3.1 Boolean Relations and their applications.

- 3.2 DeMorgan's Theorems

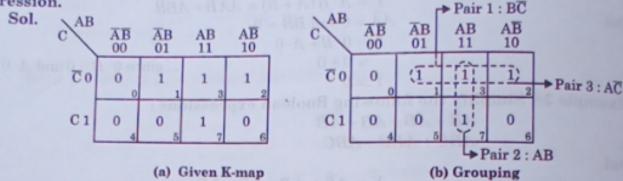

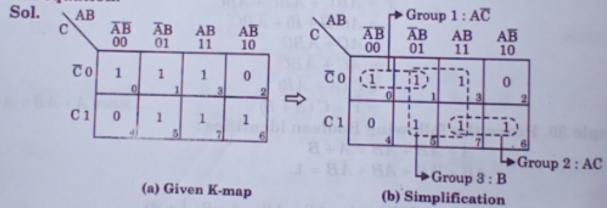

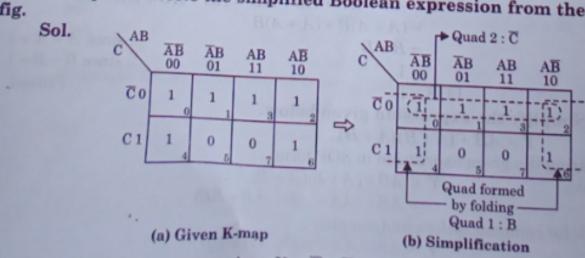

- 3.3 K-Map upto four variables

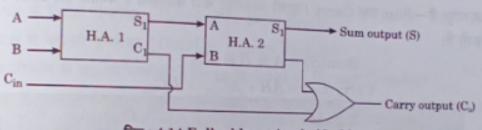

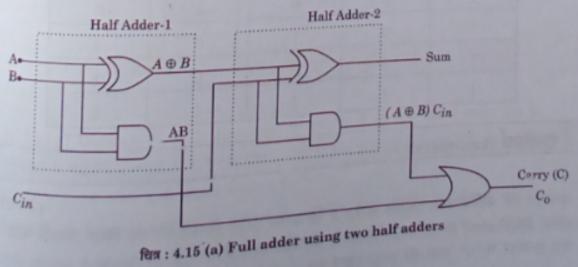

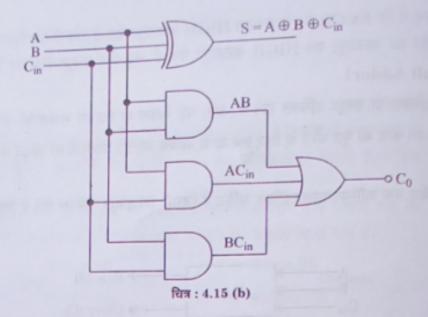

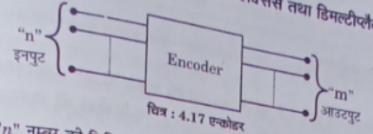

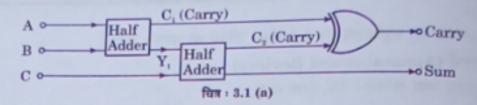

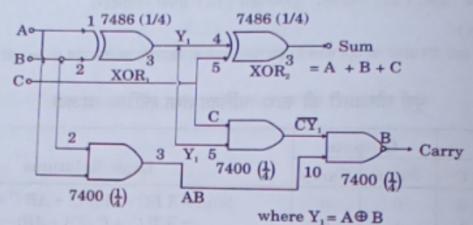

#### 4. Combinational Circuits

(12 Periods

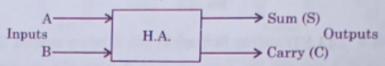

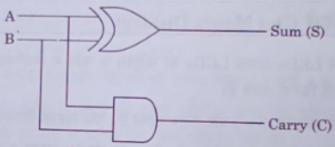

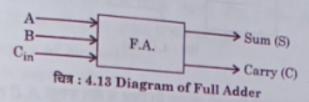

- 4.1 Half adder, Full adder

- 4.2 Encoder, Decoder

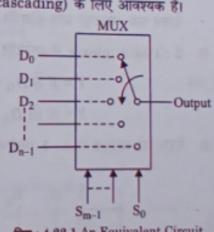

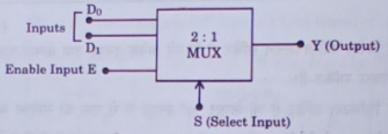

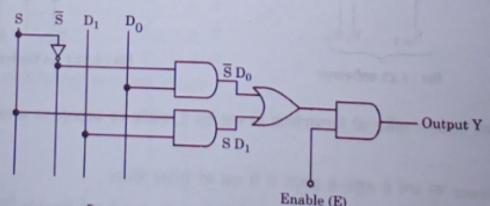

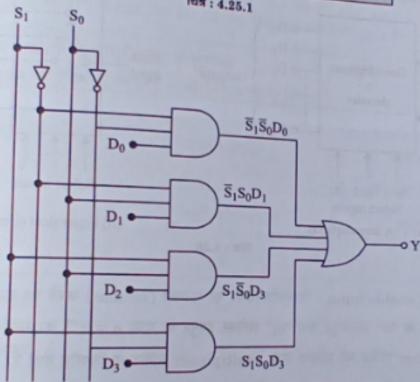

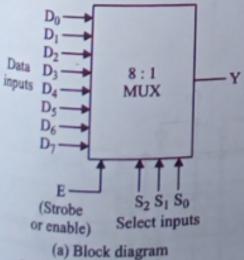

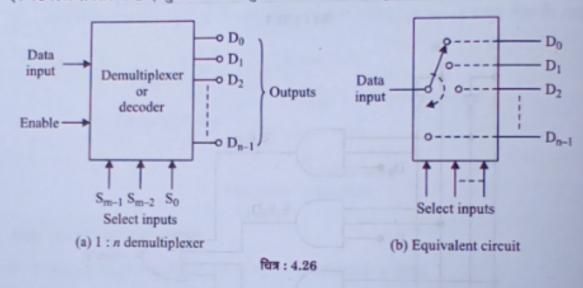

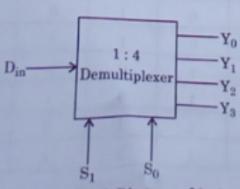

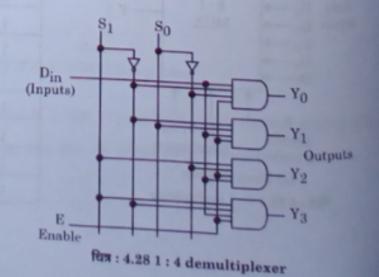

- 4.3 Multiplexer/Demultiplexer

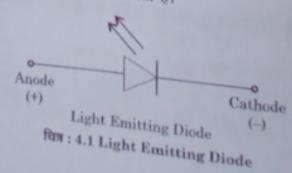

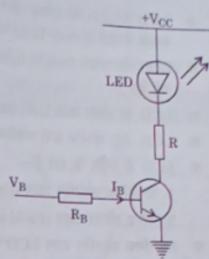

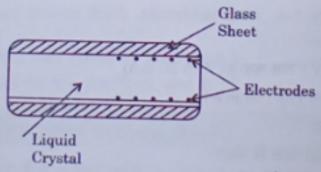

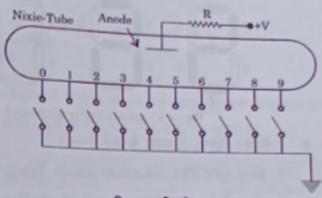

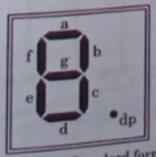

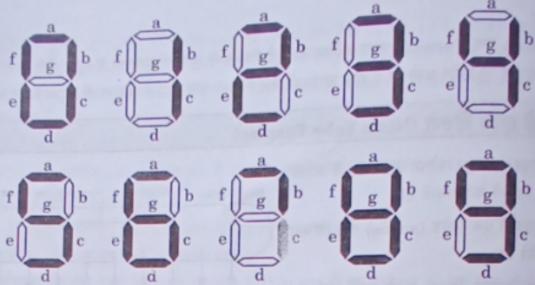

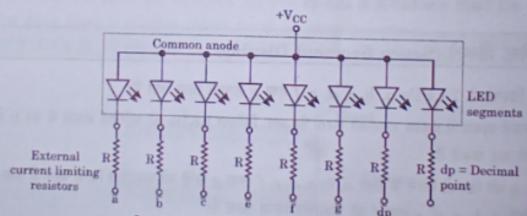

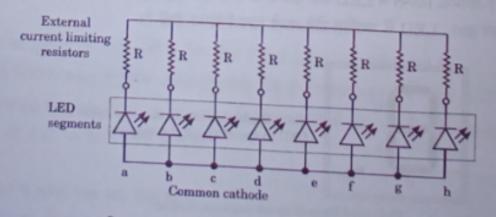

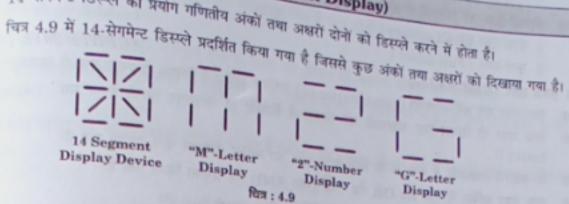

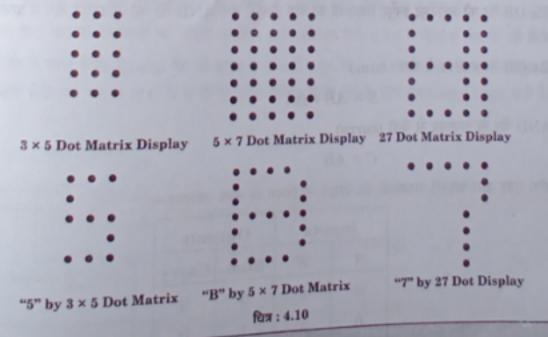

- 4.4 Display Devices (LED, LCD and 7-segment display)

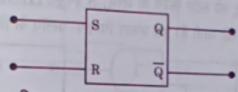

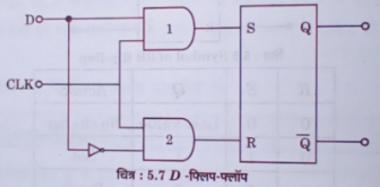

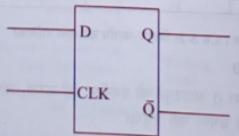

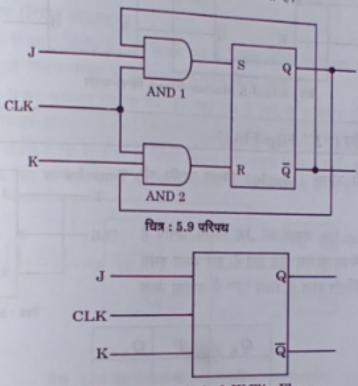

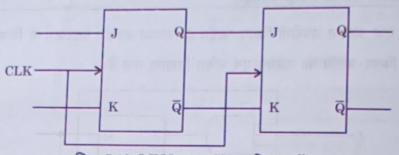

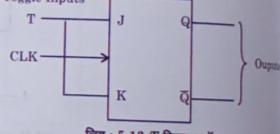

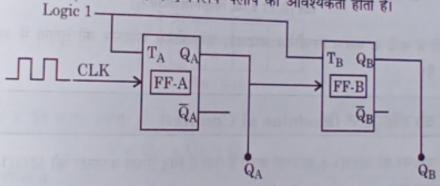

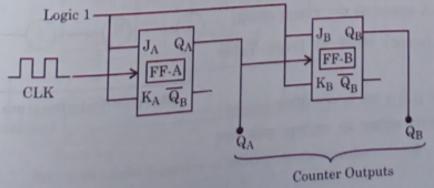

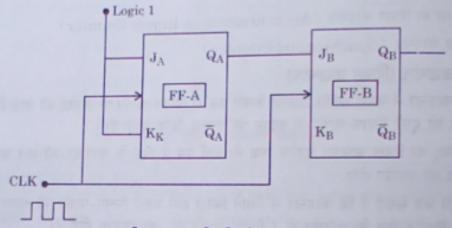

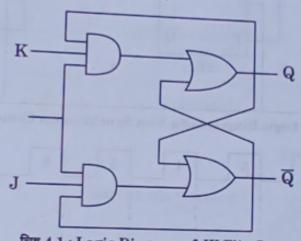

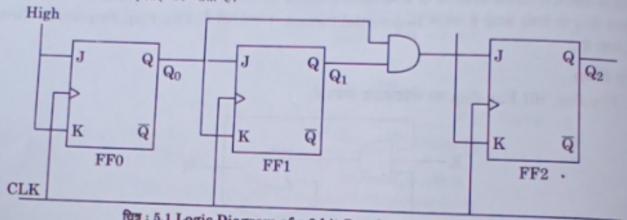

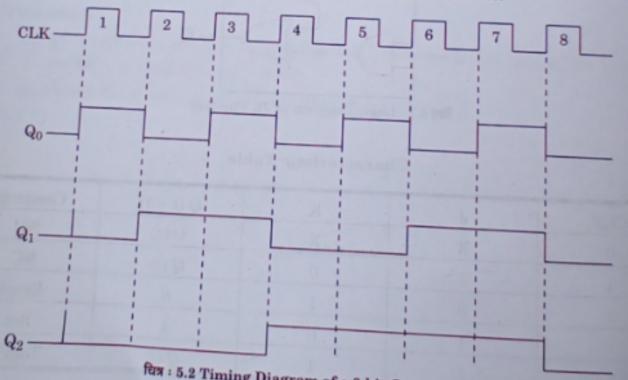

#### 5. Flip-Flops

(09 Period

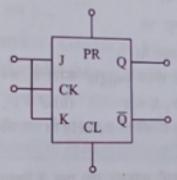

- 5.1 J-K Flip-Flop

- 5.2 R-S Flip-Flop

- 5.3 D-Type Flip-Flop

- 5.4 T-Type Flip-Flop

- 5.5 Applications of Flip-Flops

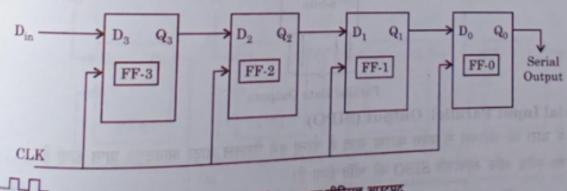

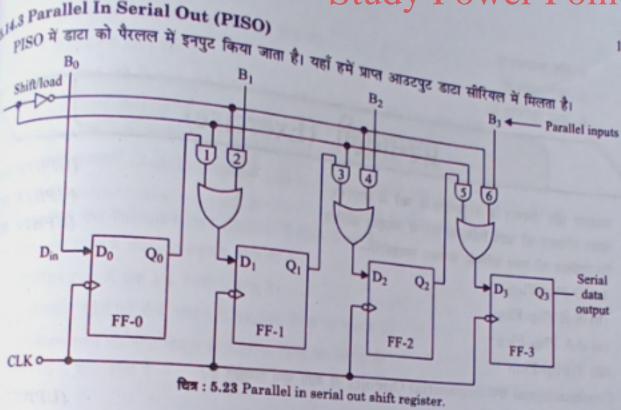

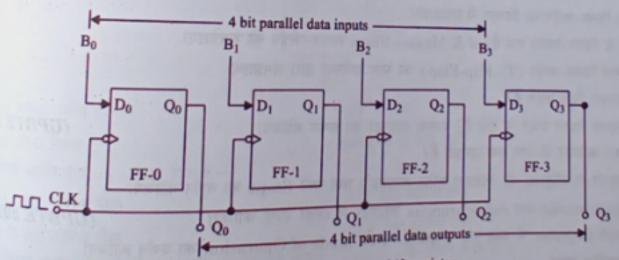

- 6. Introduction of Shift Registers and Counters

(08 Periods)

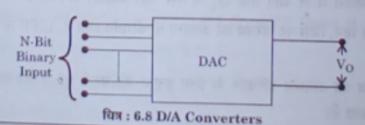

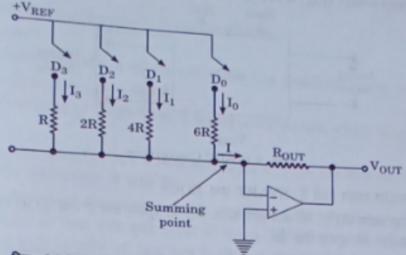

7. A/D and D/A Converters

(06 Periods)

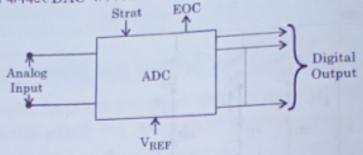

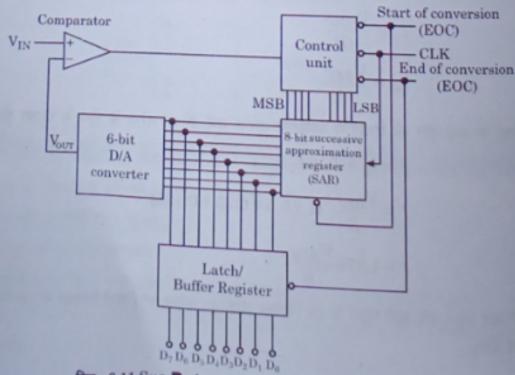

- 7.1 A/D converter (Counter, rmap, successive approximation method of A/D Conversion)

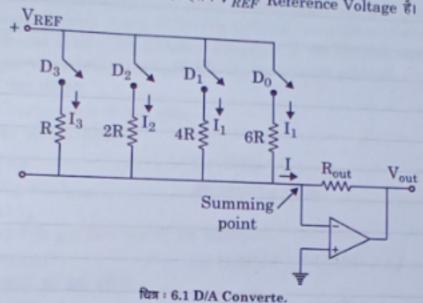

- 7.2 D/A Converters (Binary weighted, R-LR D/A Converter)

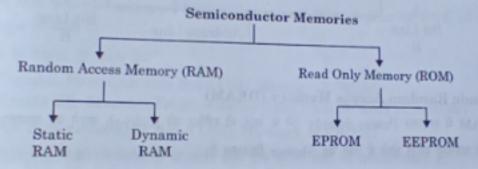

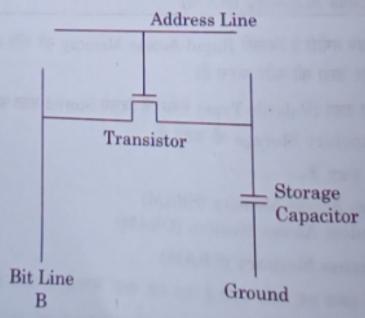

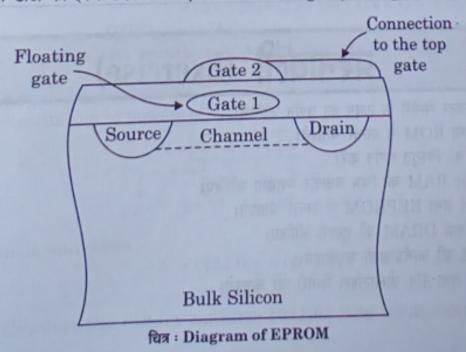

- 8. Semi-conductor Memories

(05 Periods)

- 8.1 Types of semi-conductor memories : RAM, ROM, EPROM, EEPROM

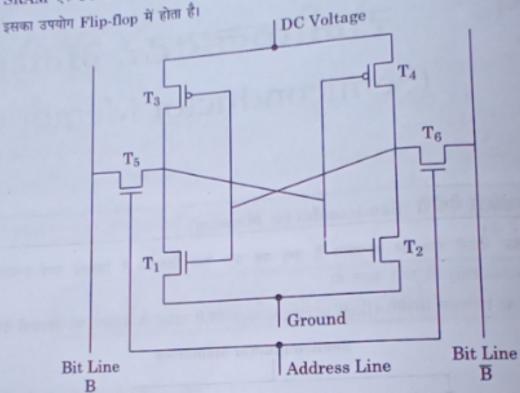

- 8.2 Static and dynamic RAM

- 8.3 Merits, demerits and applications.

#### List of Practicals

- Verification and interpretation of truth table for AND, OR, NOT, NAND, NOR, X-OR gates

- 2. Construction of Half Adder using gates

- 3. Construction of Full Adder using gates

- 4. To verify the truth table for JK flipflop

- 5. Construction and testing of any counter

- 6. Verification of operation of a 8-bit D/A converter.

# Study Power Point विषय सूची

| क्रम | अध्याय                                                                   | soul !  |

|------|--------------------------------------------------------------------------|---------|

| 1.   | डिजिटल इलेक्ट्रॉनिक्स                                                    | 1-25    |

| 2.   | लॉजिक गेट्स                                                              | 26-55   |

| 3.   | लॉजिक परिवार                                                             | 56-71   |

| 4.   | डिस्प्ले युक्तियाँ, बाइनरी एडर सर्किट, एनकोडर्स डिकोडर्स,                |         |

|      | मल्टीप्लैक्सर्स तथा डिमल्टीप्लैक्सर्स                                    | 72-88   |

|      |                                                                          |         |

|      |                                                                          |         |

| 5.   | फ्लिप-फ्लॉप                                                              | 88-104  |

|      | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स                                    | 88–104  |

| . 6. | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स                                    | 105–114 |

| . 6. | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स<br>सेमीकन्डक्टर मेमोरी             |         |

| . 6. | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स                                    | 105–114 |

| . 6. | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स<br>सेमीकन्डक्टर मेमोरी<br>परिशिष्ट | 105–114 |

| . 6. | मल्टीवाइब्रेटर तथा A/D, D/A कनवर्टर्स<br>सेमीकन्डक्टर मेमोरी<br>परिशिष्ट | 105–114 |

# अध्याय

# डिजिटल इलेक्ट्रॉनिक्स (Digital Electronics)

#### 1.1 परिचय (Introduction)

- 🚱 डिजिटल इलेक्ट्रॉनिक्स का उपयोग हम डाटा प्रोसेसिंग, कन्ट्रोल सिस्टम, संचार तथा मापन में करते हैं।

- एनेलॉग इलेक्ट्रॉनिक्स में आउटपुट वोल्टेज इनपुट वोल्टेज के अनुसार परिवर्तित होते रहते हैं अर्थात् आउटपुट वोल्टेज के अनन्त मान होते हैं।

- वह इलेक्ट्रॉनिक सर्किट जो दो स्टेट ऑपरेशन के लिए डिजाइन किया जाता है, डिजिटल सर्किट कहलाता है। इस प्रकार डिजिटल सर्किट में आउटपुट वोल्टेज की केवल दो अवस्थाएँ होती है।

- हलेक्ट्रॉनिक्स की वह ब्रांच जिसमें हम डिजिटल सर्किट का अध्ययन करते हैं, डिजिटल इलेक्ट्रॉनिक्स (digital electronics) कहलाती है।

सिग्नल को दो भागों में बाँटा गया है-

- 1. एनेलॉग सिग्नल,

- 2. डिजिटल सिग्नल।

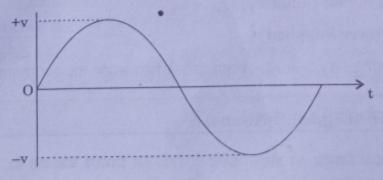

#### 1.2 एनेलॉग सिग्नल (Analog Signal)

- 🕸 एनेलॉग सिग्नल के अनन्त मान होते हैं तथा ये सिग्नल समय के साथ-साथ लगातार परिवर्तित होते रहते हैं।

- Sine wave, Triangular wave इत्यादि एनेलॉग सिग्नल के उदाहरण हैं।

चित्र : 1.1 एनेलॉग सिग्नल

#### डिजिटल इलैक्ट्रॉनिक Study Power F

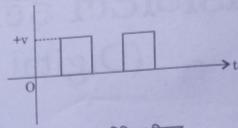

#### डिजिटल सिग्नल (Digital Signal) 1.3

डिजिटल सिग्नल के दो डिस्क्रीट स्तर (discrete level) होते हैं। यह सिग्नल सदैव Low अथवा High में से किय एक स्तर पर होता है।

चित्र : 1.2 डिजिटल सिग्नल

डिजिटल सिग्नल समय के साथ-साथ लगातार परिवर्तित नहीं होते हैं।

#### एनेलॉग सिग्नल तथा डिजिटल सिग्नल की तुलना 1.4 (Comparison of Analog Signal and Digital Signal)

(UPBTE 2013, 14, 16)

|          | पैरामीटर              | एनेलॉग सिग्नल               | डिजिटल सिग्नल        |

|----------|-----------------------|-----------------------------|----------------------|

| क्रम सं० | आउटपुट वोल्टेज के मान |                             | दो (Low अथवा High)   |

|          | नेचर                  |                             | डीस्क्रीट (Discrete) |

| 3.       | सोर्स                 | सिग्नल जनरेटर, ट्रांसड्यूसर | कम्प्यूटर            |

| 4.       | उदाहरण                | Sine wave, Triangular wave  | बाइनरी सिग्नल        |

#### एनेलॉग सिस्टम (Analog Systems) 1.5

- वह सिस्टम (System) जो एनेलॉग सिग्नल (analog signals) को प्रोसेस करता है, एनेलॉग सिस्टम कहलाता है।

- एनेलॉग सिस्टम के निम्न उदाहरण हैं-

- 1. फिल्टर (Filters),

- 2. एम्प्लीफायर (Amplifiers),

- 3. सिग्नल जेरनेटर (Signal Generators),

- 4. पावर सप्लाई (Power Supplied)।

- एनेलॉग सिस्टम की परिशुद्धता (Accuracy) कम होती है जिस कारण यह कम रिलायबल (reliable) होता है।

#### हिजिटल सिस्टम (Digital Systems) 1.6

- वह सिस्टम जो डिजिटल सिग्नल को प्रोसेस करता है, डिजिटल सिस्टम कहलाता है।

- डिजिटल सिस्टम के इनपुट एवं आउटपुट दोनों सिग्नल, डिजिटल होते हैं।

- 🕸 डिजिटल सिस्टम के निम्न उदाहरण हैं—

- 1. फ्लिप-फ्लाप (Flip-Flops),

- 2. काउन्टर (Counter),

- 3. माइक्रोप्रोसेसर (Microprocessors),

- 4. डिजिटल कैलकुलेटर (Digital Calculators),

- 5. कम्प्यूटर (Computers)।

## 1.7 डिजिटल सिस्टम के लाभ (Advantages of Digital Systems)

- 1. डिजिटल सिस्टम की परिशुद्धता (accuracy) उच्च होती है।

- 2. इन पर शोर (noise) का प्रभाव कम पड़ता है।

- 3. डिजिटल सिस्टम, एनेलॉग सिस्टम की अपेक्षा ज्यादा विश्वसनीय (reliable) होते हैं।

- 4. डिजिटल सिस्टम के बीच कम्यूनिकेशन (communication) आसानी से हो जाता है।

- 5. डिजिटल सिस्टम की डिजाइन (design)आसानी से हो जाती है।

- 6. इन पर ताप का प्रभाव बहुत कम पड़ता है।

एनेलॉग तथा डिजिटल सिग्नल का तुलनात्मक चार्ट (Comparison of Analog and Digital Systems)

|             | ( First of the Digital Di |                                                     |                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|

| क्रम<br>सं0 | पैरामीटर                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | एनेलॉग सिग्नल                                       | डिजिटल सिग्नल                                     |

| 1.          | सिग्नल प्रोसेस्ड (Signal Processed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | एनेलॉग सिग्नल                                       | डिजिटल सिग्नल                                     |

| 2.          | डिस्पले (Display)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | एनेलॉग मीटर                                         | डिजिटल डिस्पले (LED एवं LCD)                      |

| 3.          | परिशुद्धता (Accuracy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | कम                                                  | ज्यादा                                            |

| 4.          | डिजाइन (Design)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | कठिन                                                | आसान                                              |

| 5.          | मैमोरी (Memory)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | मैमोरी नहीं होती                                    | मैमोरी होती है                                    |

|             | ताप का प्रभाव (Effect of temperature)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | अधिक                                                | कम                                                |

| 7.          | शोर का प्रभाव (Effect of noise)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | अधिक                                                | कम                                                |

| 8.          | सिस्टम के बीच कम्यूनिकेशन                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | आसानी से नहीं होता                                  | आसानी से होता है                                  |

|             | (Communication between system)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |                                                   |

| 9.          | उदाहरण (Examples)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | फिल्टर, एम्प्लीफायर<br>पावर सप्लाई, सिगनल<br>जनरेटर | काउन्टर, रजिस्टर्स, माइक्रोप्रोसेसर,<br>कम्प्यूटर |

# नम्बर सिस्टम (Number System)

- डिजिटल इलेक्ट्रॉनिक्स में स्थिर संख्याओं को युग्मित कर अन्य संख्याओं को प्रदर्शित किया जाता है। 1.8

- नम्बर सिस्टम (number system) को निम्नलिखित चार भागों में बाँटा गया है— 633

- 1. डेसिमल नम्बर सिस्टम (Decimal number system) 0

- 2. बाइनरी नम्बर सिस्टम (Binary number system)

- 3. ऑक्टल नम्बर सिस्टम (Octal number system)

- 4. हेक्साडेसिमल नम्बर सिस्टम (Hexadecimal number system)

- प्रत्येक नम्बर सिस्टम के लिए एक बेस (base) होता है और प्रत्येक नम्बर सिस्टम का अधिकतम मान (late value) उसके बेस से एक कम होता है।

#### नम्बर सिस्टम और उसका बेस

| S.No. | Name of Number System | Base |

|-------|-----------------------|------|

| 1.    | Decimal               | 10   |

| 2.    | Binary                | 2    |

| 3.    | Octal                 | 8    |

| 4.    | Hexadecimal           | 16   |

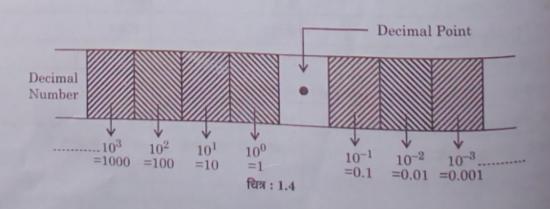

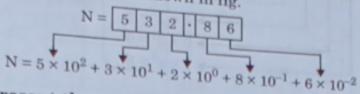

#### डेसिमल नम्बर सिस्टम (Decimal Number System) 1.9

- वह नम्बर सिस्टम जो हम प्रारम्भ से ही स्कूलों में पढ़ते चले आ रहे हैं, उसे डेसिमल नम्बर सिस्टम कहते हैं।

- डेसिमल नम्बर सिस्टम के 10 विशेष प्रतीक होते हैं, 0, 1, 2, 3, 4, 5, 6, 7, 8 तथा 9.

- डेसिमल नम्बर का बेस 10 होता है तथा इसकी अधिकतम संख्या 9 होती है।

- ऊपर दिए गए चित्र के द्वारा हम डेसिमल नम्बर को प्रदर्शित करने का अध्ययन करेंगे।

- डेसिमल प्रणाली में लिखी गई प्रत्येक संख्या के प्रत्येक गुणक का अपना एक स्थानीय मान (weighted value) है। प्रत्येक संख्या के स्थानीय मान को चित्र में प्रदर्शित किया के कि है। प्रत्येक संख्या के स्थानीय मान को चित्र में प्रदर्शित किया गया है।

डिजिटल इलेक्ट्रॉनिक्स

5

## MSD (Most Significant Digit)

बायीं तरफ की वह संख्या जिसका स्थानीय मान अधिकतम होता है, MSD कहलाती है।

#### LSD (Least Significant Digit)

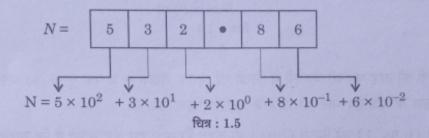

दायीं तरफ की वह संख्या जिसका स्थानीय मान सबसे कम होता है, LSD कहलाती है। उदाहरण—डेसिमल नम्बर 532.86 को प्रदर्शित करना। हल—

इस प्रकार दी गई संख्या 532.86 को प्रदर्शित किया जा सकता है।

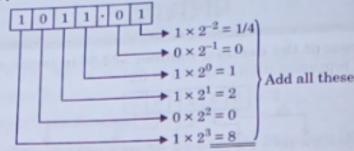

#### 1.10 बाइनरी नम्बर सिस्टम (Binary Number System)

- बाइनरी नम्बर सिस्टम के दो विशेष प्रतीक होते हैं─0 तथा 1.

- बाइनरी नम्बर सिस्टम, डेसिमल नम्बर सिस्टम की तरह कार्य करता है। इनमें विशेष अन्तर केवल बेस का है। बाइनरी नम्बर का बेस 2 होता है, जब्िक डेसिमल नम्बर का बेस 10 होता है।

#### 1.10.1 बाइनरी संख्या को डेसिमल में परिवर्तित करना

बाइनरी संख्या को डेसिमल में बदलने के लिए बाइनरी संख्या के प्रत्येक अंक को  $2^{n-1}$  से गुणा किया जाता है, जहाँ n बाइनरी संख्या के उस अंक की स्थिति को प्रदर्शित करता है। तत्पश्चात् सभी गुणनफलों को जोड़कर बाइनरी संख्या के तुल्य डेसिमल संख्या जात की जा सकती है।

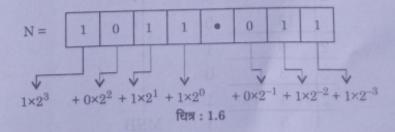

उदाहरण— बाइनरी नम्बर 1011.011 का डेसिमल तुल्यांक ज्ञात करना।

हल-Step 1: दी गयी बाइनरी संख्या को 2 के पावर के रूप में प्रदर्शित करने पर

Step 2: डेसिमल तुल्यांक

$$N = (1 \times 2^{3}) + (0 \times 2^{2}) + (1 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3})$$

$$N = (1 \times 8) + (0 \times 4) + (1 \times 2) + (1 \times 1) + (0 \times 0.5) + (1 \times 0.25) + (1 \times 0.125)$$

$$N = 8 + 2 + 1 + 0.5 + 0.25 + 0.125$$

$$N = (11.375)_{10}$$

6

- बाइनरी नम्बर का बेस 2 होता है, अत: इसकी अधिकतम संख्या 1 होती है।

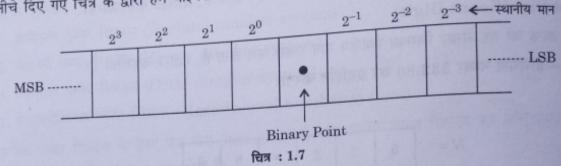

- नीचे दिए गए चित्र के द्वारा हम बाइनरी नम्बर को प्रदर्शित करने का अध्ययन करेंगे।

- डेसिमल प्रणाली की तरह बाइनरी प्रणाली में लिखी गई प्रत्येक संख्या के प्रत्येक गुणक का अपना एक स्थानीय मान होता है। प्रत्येक संख्या के स्थानीय मान को चित्र में प्रदर्शित किया गया है।

- बाइनरी डिजिट (0 तथा 1) को बिट्स (bits) भी कहते हैं। अतः हम कह सकते हैं कि बाइनरी सिस्टम 2-बिट सिस्टम

- बायों तरफ की वह बिट जिसका स्थानीय मान अधिकतम होता है, Most Significant Bit (MSB) कहलाती है।

- दायीं तरफ की वह बिट जिसका स्थानीय मान सबसे कम होता है, Least Significant Bit (LSB) कहलाती है।

#### 1.10.2 डेसिमल संख्या को बाइनरी में परिवर्तित करना

- डेसिमल संख्या को बाइनरी में परिवर्तित करने के लिए डेसिमल संख्या को लगातार 2 से विभाजित किया जाता है।

- प्रत्येक विभाजन के पश्चात् शेषफल को रिकॉर्ड किया जाता है।

- बाइनरी संख्या प्राप्त करने के लिए सभी शेषफलों को उल्टे क्रम में लिखते हैं। उदाहरण— (105)10 को बाइनरी में परिवर्तित करना। हल-

| 2 | 105 ← |     | दी हुई संख्या |

|---|-------|-----|---------------|

| 2 | 52    | 1   | LSB           |

| 2 | 26    | 0   | 1             |

| 2 | 13    | 0   |               |

| 2 | 6     | 1   |               |

| 2 | 3     | 0   |               |

| 2 | 1     | 1   |               |

|   | 0     | 1   | MSB           |

|   |       | शेष |               |

शेषफलों को उल्टे क्रम में लिखने पर  $(105)_{10} = (1101001)_2$

$$(85)_{10} = (1010_{101})_{2}$$

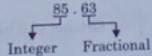

Step 3: भिन्न को बाइनरी में बदलना

$$0.63 \times 2 = 1.26 \quad 1 \quad \text{MSB}$$

$$0.26 \times 2 = 0.52 \quad 0$$

$$0.52 \times 2 = 1.04 \quad 1$$

$$0.04 \times 2 = 0.08 \quad 0$$

$$0.08 \times 2 = 0.16 \quad 0$$

$$\uparrow \quad \text{LSB}$$

शेष

$$(0.63)_{10} = (10100)_2$$

Step 4: Step 2 और Step 3 के परिणाम को मिलाने पर

$(85.63)_{10} = (1010101.10100)_2$

#### ऑक्टल नम्बर सिस्टम (Octal Number System) 1.11

- ऑक्टल नम्बर सिस्टम का बेस "8" है।

- ऑक्टल नम्बर सिस्टम के प्रत्येक डिजिट के विभिन्न मान हैं जो 0 से 7 तक होते हैं।

(0, 1, 2, 3, 4, 5, 6, and 7)

- ऑक्टल नम्बर की अधिकतम डिजिट का मान 7 होता है।

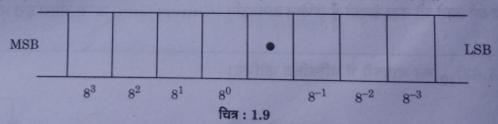

- नीचे दिए गए चित्र के द्वारा हम ऑक्टल नम्बर को प्रदर्शित करने का अध्ययन करेंगे।

डेसिमल तथा बाइनरी संख्या की तरह ऑक्टल प्रणाली में भी प्रत्येक संख्या के प्रत्येक गुणांक का अपना एक स्थान होता है। प्रत्येक संख्या के स्थानीय मानों को चित्र में प्रदर्शित किया गया है।

#### 1.11.1 ऑक्टल संख्या को डेसिमल में परिवर्तित करना

ऑक्टल संख्या को डेसिमल में बदलने के लिए ऑक्टल संख्या के प्रत्येक अंक को  $8^{n-1}$  से गुणा किया जाता है ऑक्टल संख्या के उस अंक की स्थिति को प्रदर्शित करता है। तत्पश्चात् सभी गुणनफलों को जोड़कर ऑक्टल संख्या डेसिमल संख्या प्राप्त की जाती है।

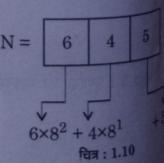

उदहारण—ऑक्टल संख्या 645 का डेसिमल तुल्यांक ज्ञात करना।

हल-

Step 1: दिए गए ऑक्टल संख्या को 8 के पावर के रूप में प्रदर्शित करने पर N =

Step 2: डेसिमल तुल्यांक

$$N = (6 \times 8^{2}) + (4 \times 8^{1}) + (5 \times 8^{0})$$

$$N = (6 \times 64) + (4 \times 8) + (5 \times 1)$$

$$N = (421)_{10}$$

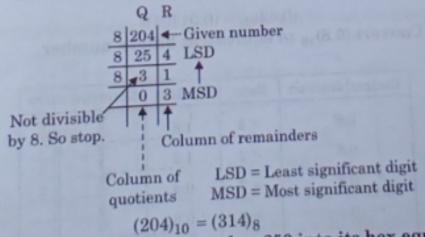

1.11.2 डेसिमल संख्या को ऑक्टल में परिवर्तित करना

डेसिमल संख्या को ऑक्टल संख्या में परिवर्तित करने के लिए डेसिमल संख्या को 8 से लगातार भाग दिया जाता है तथा प्रत्येक विभाजन की क्रिया के पश्चात् प्राप्त शेषफलों को उल्टे क्रम में लिखने पर हमें ऑक्टल संख्या प्राप्त हो जाती है।

उदाहरण— डेसिमल संख्या (204) 10 को ऑक्टल में परिवर्तित करना।

शेषफलों को उल्टे क्रम में लिखने पर (204)10 = (314)8.

न्टल संख्या को बाइनरी में परिवर्तित करना

अवि चंख्या का बेस "8" होता है। अतः इसकी अधिकतम मान की संख्या 7 होती है।

अॉक्टल संख्या प्रत्येक डिजिट (0, 1, 2, ...... 7) के लिए बाइनरी तुल्यांक निश्चित होता है,

| Octal | Equivalent<br>Binary Number |

|-------|-----------------------------|

| 0     | 000                         |

| 1     | 001                         |

| 2     | 010                         |

| 3     | 011                         |

| 4     | 100                         |

| 5     | 101                         |

| 6     | 110                         |

| 7     | 111                         |

चित्र : 1.12 ऑक्टल नम्बर का बाइनरी तुल्यांक

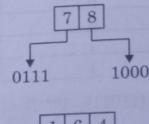

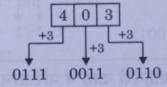

उदाहरण— ऑक्टल संख्या (364) $_8$  को बाइनरी में परिवर्तित कीजिए। हल— दी हुई ऑक्टल संख्या = 364

🕸 प्रत्येक संख्या का बाइनरी तुल्यांक लिखने पर

# Study Power Poissing schapillage

| 3   | 6   | 4   |

|-----|-----|-----|

| 011 | 110 | 100 |

🥸 अत: दी हुई ऑक्टल संख्या का बाइनरी तुल्यांक

$(364)_8 = (011110100)_2$

#### 1.11.4 बाइनरी संख्या को ऑक्टल संख्या में परिवर्तित करना

अ बाइनरी संख्या को ऑक्टल में परिवर्तित करने के लिए LSB से प्रारम्भ कर 3-3 बिट्स के समूह बनाए जाते हैं उसके बाद प्रत्येक समूह के लिए उसके तुल्य ऑक्टल संख्या लिख दी जाती है।

उदहारण— बाइनरी संख्या (11010010) $_2$  को ऑक्टल संख्या में परिवर्तित कीजिये।

${\bf Em}$ — दी हुई बाइनरी संख्या = 11010010

3-3 बिट का समूह बनाने पर

यहाँ दी हुई संख्या के ग्रुप 3 में तीन का समूह बनाने के लिए 0 को आगे लगा देते हैं। ऑक्टल तुल्यांक = 322

$(11010010)_2 = (322)_8$

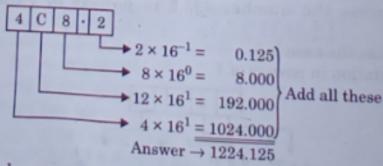

### 1.12 हेक्साडेसिमल नम्बर सिस्टम (Hexadecimal Number % stem)

- 🕸 हेक्साडेसिमल नम्बर सिस्टम का बेस "16" होता है।

- 😩 हेक्साडेसिमल नम्बर की अधिकतम डिजिट का मान 15 होता है।

- हेक्साडेसिमल नम्बर में कुल 16 संख्याएँ आती हैं जिनमें 0 से 9 तक सभी डिजिट तथा अंग्रेजी वर्णमाला के अक्षर A, B, C, D, E और F आते हैं।

- # नीचे हेक्साडेसिमल नम्बर की सभी डिजिट एवं उसके मान को दर्शाया गया है─

| Hexadecimal Digit | Value |

|-------------------|-------|

| 0                 | 0     |

| 1                 | 1     |

| 2                 | 2     |

| 3                 | 3     |

| 4                 | 4     |

| 5                 | 5     |

|   | NAME AND ADDRESS OF THE OWNER, WHEN PERSONS AND ADDRESS O |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| В | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| E | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

चित्र : 1.14 हेक्साडेसीमल डिजिट का मान

#### 1.12.1 हेक्साडेसिमल को डेसिमल में परिवर्तित करना

n हेक्साडेसिमल को डेसिमल में परिवर्तित करने के लिए हैक्साडेसिमल के प्रत्येक अंक को  $16^{n-1}$  से गुणा किया जाता है जहाँ n हेक्साडेसिमल नम्बर की उस अंक की स्थिति को प्रदर्शित करता है उसके बाद सभी गुणनफलों को जोड़कर हेक्साडेसिमल नम्बर के तुल्य डेसिमल नम्बर प्राप्त हो जाता है।

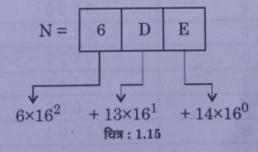

#### उदहारण—हेक्साडेसिमल नम्बर 6DE का डेसिमल तुल्यांक ज्ञात कीजिए।

हल- Step 1: दी गयी हेक्साडेसिमल संख्या को 16 के पावर के रूप में प्रदर्शित करना।

#### Step 2: डेसिमल तुल्यांक

$$N = 6DE = (6 \times 16^{2}) + (132 \times 16^{1}) + (14 \times 16^{0})$$

$$N = (6 \times 256) + (13 \times 16) + (14 \times 1)$$

$$N = (1758)_{10}$$

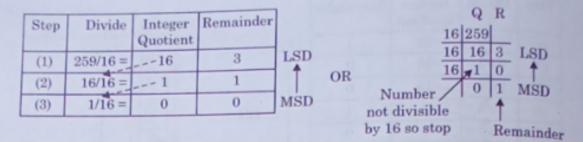

#### अतः $(6DE)_{16} = (1758)_{10}$ 1.12.2 डेसिमल संख्या को हेक्साडेसिमल में परिवर्तित करना

डेसिमल संख्या को हेक्साडेसिमल में परिवर्तित करने के लिए डेसिमल संख्या को 16 से लगातार भाग दिया जाता है तथा प्रत्येक विभाजन की क्रिया के पश्चात् शेषफलों को उल्टे क्रम में लिखने पर हमें हेक्साडेसिमल संख्या प्राप्त हो जाती है।

शेषफलों को उल्टे क्रम में लिखने पर

$$(259)_{10} = (103)_{16}$$

# 1.12.3 हेक्साडेसिमल संख्या को बाइनरी में परिवर्तित करना

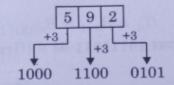

हेक्साडेसिमल के प्रत्येक अंक के लिए (0,1,2,.....,9) तथा A, B, C, D, E, F का बाइनरी तुल्यांक निश्कि जो नीचे दर्शाया गया है-

| गया ह—                | Equivalent    |

|-----------------------|---------------|

| Hexadecimal<br>Number | Binary Number |

| 0                     | 0000          |

| 1                     | 0001          |

| 2                     | 0010          |

| 3                     | 0011          |

| 4                     | 0100          |

| 5                     | 0101          |

| 6                     | 0110          |

| 7                     | 0111          |

| 8                     | 1000          |

| 9                     | 1001          |

| A                     | 1010          |

| В                     | 1011          |

| C                     | 1100          |

| D                     | 1101          |

| E                     | 1110          |

| F                     | 1111          |

|                       | 1 1 1 1       |

चित्र : 1.17 हेक्साडेसिमल का बाइनरी तुल्यांक

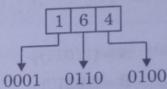

उद्हारण—हेक्स संख्या AFB2 को बाइनरी में परिवर्तित कीजिए। हल-दी हुई संख्या के प्रत्येक अंक का बाइनरी तुल्यांक लिखने पर

| THE RESERVE AND ADDRESS OF THE PERSON NAMED IN COLUMN 1 |      |      |      |

|---------------------------------------------------------|------|------|------|

| A                                                       | F    | В    | 2    |

| 1010                                                    | 1111 | 1011 | 0010 |

|                                                         |      |      | 0010 |

अतः दी हुई हेक्स संख्या का बाइनरी तुल्यांक

$(AFB2)_{16} = (1010111110110010)_2$

#### 1.12.4 बाइनरी संख्या को हेक्साडेसिमल में परिवर्तित करना

बाइनरी संख्या को हेक्साडेसिंमल में परिवर्तित करने के लिए LSB से प्ररम्भ करके 4-4 बिट्स का समूह बनाया जाता है उसके बाद प्रत्येक समूह के लिए उसके तुल्य हेक्स संख्या लिख दी जाती है।

उदहारण—बाइनरी संख्या  $(1100010111100010)_2$  का हेक्स तुल्यांक ज्ञात कीजिए।

हल— दी हुई संख्या के अंकों का 4-4 बिट का समृह बनाने पर

Group 4 Group 3 Group 2 Group 1

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \downarrow$$

C 5 E 2

अतः दी हुई संख्या का हेक्स तुल्यांक  $=(C5E2)_{16}$

$(11000101111100010)_2 = (C5E2)_{16}$

#### 1.12.5 हेक्साडेसिमल संख्या को ऑक्टल में परिवर्तित करना

☼ हेक्साडेसिमल संख्या को ऑक्टल संख्या में परिलर्तित करने के लिए पहले हेक्साडेसिमल संख्या को बाइनरी में परिवर्तित करते हैं, उसके बाद प्राप्त बाइनरी संख्या को ऑक्टल संख्या में परिवर्तित करते हैं।

उदाहरण—हेक्साडेसिमल (25B)<sub>16</sub> का ऑक्टल तुल्यांक ज्ञात कीजिए।

हल-Step 1: दी हुई हेक्साडेसिमल संख्या का बाइनरी तुल्यांक

| 2    | 5    | В    |

|------|------|------|

| 0010 | 0101 | 1011 |

प्राप्त बाइनरी संख्या = 001001011011

Step 2: बाइनरी संख्या का ऑक्टल तुल्यांक

| 001 | 001 | 011 | 011 |

|-----|-----|-----|-----|

| 1   | 1   | 3   | 3   |

अतः दी हुई हेक्साडेसिमल संख्या का ऑक्टल तुल्यांक =(1133)8

$(25B)_{16} = (1133)_8$

#### 1.12.6 ऑक्टल संख्या से हेक्साडेसिमल संख्या प्राप्त करना

आक्टल संख्या से हेक्साडेसिमल संख्या प्राप्त करने के लिए सर्वप्रथम ऑक्टल संख्या को बाइनरी में परिवर्तित करते हैं तथा प्राप्त बाइनरी संख्या से हेक्साडेसिमल संख्या प्राप्त की जाती है।

उदाहरण—ऑक्टल संख्या (615)8 का हेक्स तुल्यांक ज्ञात करना।

हल- Step 1: दी हुई ऑक्टल संख्या का बाइनरी तुल्यांक

| 6   | 1   | 5   |

|-----|-----|-----|

| 110 | 001 | 101 |

# Study Power Point इलीकट्रॉनिक्स

14

प्राप्त बाइनरी संख्या = 110001101

Step 2 : बाइनरी संख्या का हेक्स तुल्यांक

0001

1000

1101 D

अतः दी गई बाइनरी संख्या का हेक्स तुल्यांक  $(18D)_{16}$   $(615)_{8} = (18D)_{16}$

#### 1.13 बाइनरी अर्थमेटिक (Binary Arithmetic)

- 🕸 कम्प्यूटर सर्किट डेसिमल नम्बर को प्रोसेस नहीं करता, यह केवल बाइनरी नम्बर को प्रोसेस करता है।

- अबाइनरी एडिशन (Binary Addition) सभी प्रकार के अन्य ऑपरेशन जैसे—बाइनरी सबट्रेक्शन, मल्टीप्लिकेशन तथा डिविजन के लिए कुंजी (key) का कार्य करती है। अत: हम सर्वप्रथम बाइनरी एडिशन (Binary Addition) का अध्ययन करेंगे।

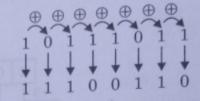

#### बाइनरी एडिशन के नियम (Rules for Binary Addition)

बाइनरी संख्या को जोड़ने पर हमें आउटपुट SUM तथा CARRY प्राप्त होता है जो नीचे सत्य तालिका में दर्शाया गया है—

| A | В | SUM | CARRY |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

उदाहरण—बाइनरी संख्या  $(10111)_2$  तथा  $(11001)_2$  का योग प्राप्त कीजिए। हल—दी हुई बाइनरी संख्या A तथा B का योग

| Car  | rry→ 1                | 1 | 1 | 1 |   |  |

|------|-----------------------|---|---|---|---|--|

| A    | $\rightarrow$ 1       | 0 | 1 | 1 | 1 |  |

| H    | 3→ 1                  | 1 | 0 | 0 | 1 |  |

| Ansv | $ver \rightarrow 1$ 1 | 0 | 0 | 0 | 0 |  |

अतः दी हुई बाइनरी संख्या का योग  $=(110000)_2$

उदाहरण—बाइनरी संख्या  $(11000)_2$  तथा  $(1101)_2$  का योग प्राप्त कीजिए। हल—दी हुई बाइनरी संख्या का योग

अतः दी हुई बाइनरी संख्या का योग  $=(100101)_2$

#### 1.14 बाइनरी सबट्रेक्शन (Binary Subtraction)

बाइनरी सबट्रेक्शन के लिए दी गई तालिका के नियमों का पालन करते हैं।

| A | В | SUB | BORROW |

|---|---|-----|--------|

| 0 | 0 | 0   | 0      |

| 1 | 0 | 1   | 0      |

| 1 | 1 | 0   | 0      |

| 0 | 1 | 1   | 1      |

उदाहरण—बाइनरी संख्या  $A=(11011)_2$  तथा  $B=(10110)_2$  को सबट्रेक्ट कीजिए। हल—दी गई बाइनरी संख्या

$$A = (11011)_{2}$$

$$B = (10110)_{2}$$

$$A \rightarrow 1 \qquad 1 \qquad 0 \qquad 1 \qquad 1$$

$$B \rightarrow 1 \qquad 0 \qquad 1 \qquad 1 \qquad 0$$

$$Answer \qquad 0 \qquad 0 \qquad 1 \qquad 0 \qquad 1$$

अतः दी गई बाइनरी संख्या का सबट्रेक्शन =  $(00101)_2$

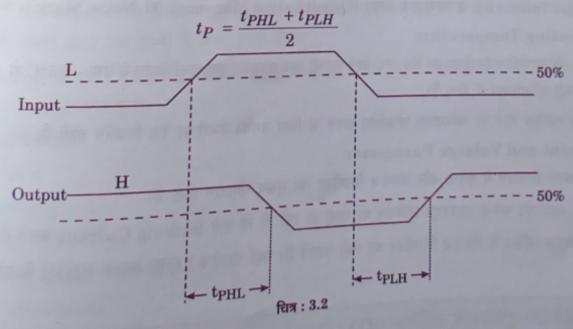

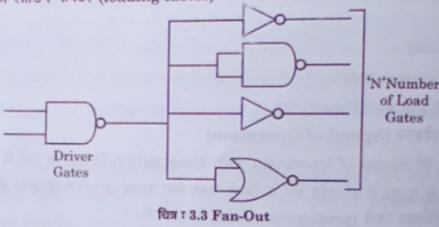

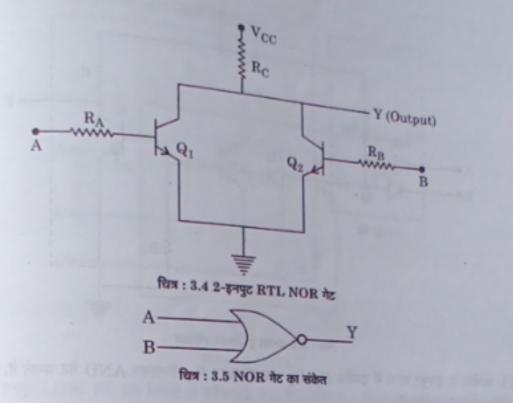

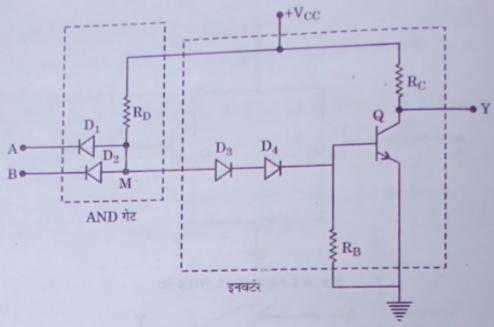

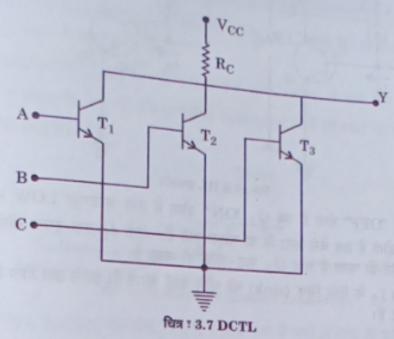

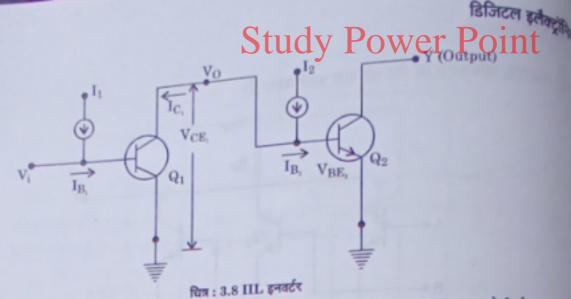

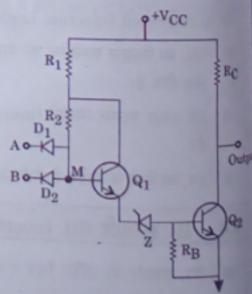

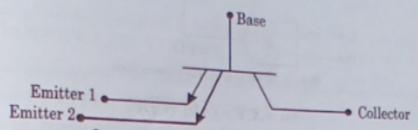

#### 1.15 बाइनरी कोडेड दशमलव [Binary Coded Decimal (BCD) Code]